题目

Integrated Computer Systems (082025-NRL)

单项选择题

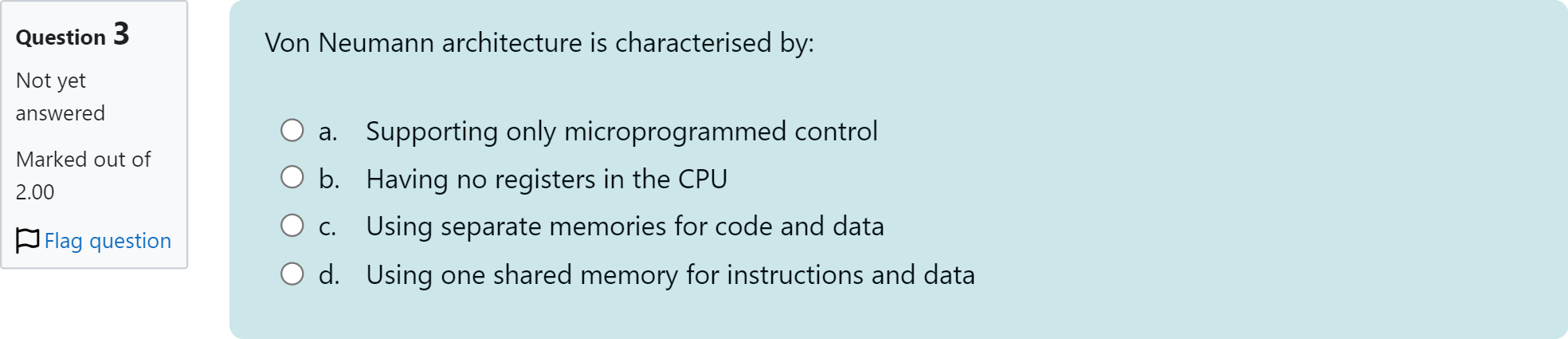

Von Neumann architecture is characterised by:

选项

A.a. Supporting only microprogrammed control

B.b. Having no registers in the CPU

C.c. Using separate memories for code and data

D.d. Using one shared memory for instructions and data

查看解析

标准答案

Please login to view

思路分析

The question asks you to identify a defining feature of Von Neumann architecture among the given choices.

Option a: 'Supporting only microprogrammed control' — This is not a defining trait of Von Neumann architecture. Microprogrammed control refers to how control s......Login to view full explanation登录即可查看完整答案

我们收录了全球超50000道考试原题与详细解析,现在登录,立即获得答案。

类似问题

Which of the following statements is true about Von Neumann Architecture?

Which of the following statements best describes CISC architecture?

In the Harvard Architecture, which of the following is separate?

Question textCompare the two architectures (Von Neumann and Harvard) by selecting the correct characteristics for each aspect. (8 marks) 1. Memory Organization In the Von Neumann architecture, data and instructions are stored in a: Answer 1 Question 34[select: , Single shared memory for both data and instructions, Separate memory for data only, Separate memory for instructions only, Independent caches] In the Harvard architecture, data and instructions are stored in: Answer 2 Question 34[select: , Separate memories for data and instructions, One shared memory, Virtual memory only, Secondary storage] 2. Bus ConfigurationVon Neumann architecture uses: Answer 3 Question 34[select: , A single bus for both data and instructions (bottleneck), Two independent buses, A wireless bus, A segmented bus system] Harvard architecture uses: Answer 4 Question 34[select: , Separate instruction and data buses, One shared bus, An external bus only, A cached instruction bus only] 3. Instruction/Data FlowInstruction and data in Von Neumann architecture travel through: Answer 5 Question 34[select: , The same pathway, Separate pipelines, Dedicated execution buffers, Read-only bus] Instruction and data in Harvard architecture travel through: Answer 6 Question 34[select: , Independent pathways, Shared execution lanes, Cache-only paths, Virtual routing] 4. Execution Efficiency Von Neumann architecture is generally: Answer 7 Question 34[select: , Slower due to the bottleneck, Faster due to dual buses, More efficient in parallel tasks, Only used in GPUs] Harvard architecture is generally: Answer 8 Question 34[select: , Faster due to parallel access, Slower due to single bus, Less efficient with branching, Dependent on virtual memory]

更多留学生实用工具

希望你的学习变得更简单

加入我们,立即解锁 海量真题 与 独家解析,让复习快人一步!