Questions

ECE260B_WI25_A00 ECE260B Midterm - Winter 2025

Multiple fill-in-the-blank

Assume the required time at output f is 5.80. Please calculate the required time for x and the origin. Note: The value inside the circle represents the delay of the gate. The value around the edge represents the delay of the wire. Required time for x: [Fill in the blank], Required time for origin: [Fill in the blank],

Options

A.4.6

B.4.60

C.0.8

D.0.80

View Explanation

Verified Answer

Please login to view

Step-by-Step Analysis

To tackle this type of timing problem, I’ll first restate what we’re given and what we’re solving for, then walk through each option to see how it fits with the overall timing goal.

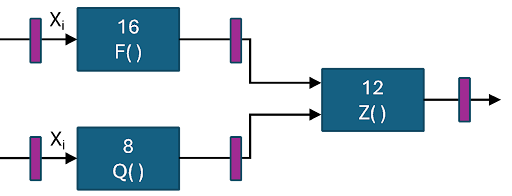

- Given: The required time at output f is 5.80 (units of time). The diagram shows a combination of gate delays and wire delays. The value inside a circle is the gate delay, while the values around the edges are wire delays. The blocks labeled F(), Q(), and Z() carry gate delays, and the purple bars along the wires carry wire delays.

- We need to determine two individual required times: one for x and one for origin, such that the total timing constraint at the output f is satisfied when all path delays (gate delays plus wire delays along the path) are accounted for.

Now, I’ll analyze the given answer options one by one in the context of the timing constraint, explaining why each is plausible or not.

Option A: x = 4.6

- If x must contribute a ......Login to view full explanationLog in for full answers

We've collected over 50,000 authentic exam questions and detailed explanations from around the globe. Log in now and get instant access to the answers!

Similar Questions

Consider the circuit below and assume the following parameters: tsetup = thold = 40 ps, tC2Q-min = 50 ps, tC2Q-max = 60 ps, Vt = 0.3V The min and maximum combinational delays (in pico seconds) through the logic blocks are shown in the figure in terms of the supply voltage VDD. Clock arrival times at each register are also given in the figure. Provide numeric answers to the following questions: 1) The minimum clock period of this circuit is [Fill in the blank] ps? 2) The maximum voltage this circuit can run is [Fill in the blank] V. Write NA (not applicable) if there is no max voltage.

Consider the following setup timing report. Fill in the boxes 1 and 2 with the right numerical values (keep 3 decimal places). 1 [Fill in the blank], 2 [Fill in the blank],

In a consumer society, many adults channel creativity into buying things

Economic stress and unpredictable times have resulted in a booming industry for self-help products

More Practical Tools for Students Powered by AI Study Helper

Making Your Study Simpler

Join us and instantly unlock extensive past papers & exclusive solutions to get a head start on your studies!